Overview

Description

About

11 Bermudiana Road

Sunnyvale, 94085, CA

United States

Latest press releases

Announces new design, verification and simulation solutions to re-engineer AI-powered product innovation at Synopsys Converge 2026

Key Highlights

- Unveiling Synopsys Multiphysics Fusion™ technology — the first in a broader roadmap of EDA solutions that integrate Synopsys and Ansys technologies for semiconductor design

- Demonstrating an industry-first L4 orchestrated, multi-agent design and verification workflow, powered by Synopsys AgentEngineer™ technology

- Launching the first major Ansys product release since acquisition, introducing new AI-driven multiphysics simulation, Synopsys technology integrations, and real-world digital twin technologies to transform simulation and analysis for smarter, more resilient systems

- Launching new hardware-assisted verification (HAV) platforms and unique, software-defined capabilities that set new performance, scalability, and flexibility benchmarks throughout the portfolio

SUNNYVALE, Calif., March 11, 2026 /PRNewswire/ -- Today, Synopsys, Inc. (Nasdaq: SNPS) opened Synopsys Converge 2026, its new flagship conference, with a keynote by Synopsys president and CEO, Sassine Ghazi, who shared his vision for a new silicon-to-systems design paradigm for the era of pervasive intelligence — one that is silicon-powered, AI-enabled, and software-defined. He also announced new engineering solutions across Synopsys' expanded portfolio to advance how innovators design, verify, and deliver next generation AI-powered products.

"The complexity of next-generation intelligent systems requires a completely new engineering approach," said Ghazi. "By integrating co-design of software and hardware, electronics and physics, by harnessing digital twins to design, test, and refine products before physical production, and using AI to enhance human capabilities, customers' R&D teams can accelerate time to market of their intelligent systems. At Synopsys Converge, we're demonstrating the power of our silicon-to-systems engineering solutions that make us the best partner for engineering the future."

Customers and partners such as AMD, Intel, Microsoft, and NVIDIA were featured during Ghazi's keynote, underscoring the need for co-design of hardware and software, silicon and systems. In addition, Synopsys, AMD and Microsoft are initiating a collaboration to enable faster access to Synopsys EDA tools on Microsoft platforms, powered by AMD compute.

Below is a summary of announcements made at Synopsys Converge.

Unveiling Multiphysics Fusion Technology: First Wave of Integrated Synopsys + Ansys Solutions for Chip Design

Synopsys announced Multiphysics Fusion technology and the first wave of EDA solutions that integrate Ansys golden multiphysics engines into Synopsys' leading EDA portfolio to solve today's pressing chip design problems caused by electromagnetics, thermal, and mechanical effects.

Voltage drop, thermal effects, and electromagnetic coupling have become critical challenges for heterogeneous designs at advanced nodes, directly affecting performance and reliability. Integrating multiphysics analysis into the design flow helps teams identify and resolve issues earlier, with greater accuracy and better correlation to final signoff. This reduces design iterations and improves power, performance, and area (PPA) metrics — transforming the process from overdesign to co-design. The first solutions to incorporate Multiphysics Fusion technology address:

- Timing Signoff: Integrating voltage drop awareness and thermal analysis provides signoff for extreme operating conditions and stringent reliability requirements to accelerate time-to-signoff.

- Multi-Die Design: Offering thermal analysis and power integrity optimization across the full EDA stack from early floorplanning to signoff, in addition to high-speed auto-routing with AI-driven signal integrity optimization enables early thermal, IR, and stress analysis.

- Design Closure: Incorporating thermal and voltage-drop awareness speeds design closure via faster late-stage bug fixes, reducing design iterations, and improving PPA.

- Analog & Mixed Signal Design: Enabling greater electromagnetics accuracy and faster power integrity analysis for reliable analog design.

These first Multiphysics Fusion capabilities are now in active beta engagements with early access customers with production availability expected in the coming months.

Ushering in a New Chip Design Paradigm with AgentEngineer Technology

Synopsys is pioneering AI capabilities with increasing levels of autonomy across its leading EDA solutions. Beginning with reinforcement learning, followed by generative AI capabilities delivered in Synospys.ai™, the company is now building an open agentic AI stack centered on orchestrated, multiagent workflows to address use cases from silicon to systems.

Today, Synopsys unveiled an industry-first L4 agentic workflow for design and verification. Powered by AgentEngineer technology, the new adaptive learning, multi-agent orchestrated system demonstrates how agentic AI can augment human engineers and accelerate highly complex chip design tasks beyond traditional methods.

The workflow features intelligent orchestration across multiple Synopsys EDA agents with adaptive learning to: generate Register Transfer Level (RTL) code from natural language and formal specification, run Lint checks to ensure clean RTL, generate unit-level testbenches, and finally iteratively run verification with EDA tools to converge on target objectives. This front-end design process typically takes a team of verification engineers four to six months for a large SoC design using traditional methods. The Synopsys AgentEngineer-powered workflow is already helping customers improve productivity by 2x, with improvements as high as 5x observed in select cases.

Synopsys' agentic stack is built on industry standard SDKs and APIs to be interoperable with existing customer agents and data. The company is collaborating with industry leaders like AMD, Microsoft — including its Foundry and Discovery platforms, and NVIDIA to develop differentiated, agentic capabilities with increasing levels of autonomy over time. Synopsys is currently engaging with customers on this first multi-agent workflow and is committed to delivering additional, orchestrated, multi-agent workflows for the entire design-to-manufacturing flow.

To see the new design and verification workflow in action, watch: Accelerate Innovation with First Orchestrated Multi-Agent Workflow for Chip Design.

Synopsys Launches the First Major Ansys Product Release Since Acquisition

Synopsys today introduced the latest updates to the industry's deepest and broadest simulation portfolio, which feature integrated workflows across materials intelligence, functional safety, photonics design, and embedded systems. Marking the first major Ansys product release since the acquisition closed, Ansys 2026 R1 delivers:

- New agentic and generative AI simulation capabilities, with the new Mesh Agent feature in Ansys Mechanical™ software; Ansys GeomAI, a new solution for generating, evaluating, and refining geometry concepts; and Discovery Validation Agent, an agentic AI partner that can proactively identify setup issues using contextual intelligence and industry best practices.

- Synopsys technology integrations including Synopsys VC Functional Safety Manager (VC FSM) and Ansys medini® analyze™ software, creating an end‑to‑end workflow linking system‑ and chip‑level safety analysis to automate traceability and eliminate manual data sharing; Synopsys QuantumATK® and the Ansys Granta MI® platform to integrate atomic‑scale materials modeling with enterprise materials management to create consistent, simulation‑ready materials records; and Synopsys OptoCompiler™ and Ansys Lumerical FDTD™ software, connecting photonic device design to system‑level optical simulation with automated Verilog‑A model generation and consistent optical behavior.

Enhancements across Synopsys' simulation and analysis solutions enable engineers to harvest trusted simulation results with more speed and precision, further shrinking the gap between simulation and physical testing. To learn more, read the press release: Synopsys Launches Ansys 2026 R1 to Re-Engineer Engineering with Joint Solutions and AI-Powered Products.

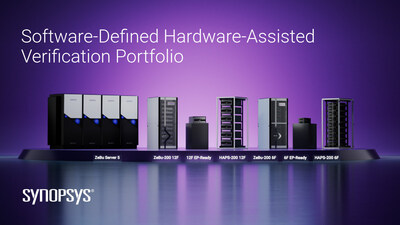

Introducing New Software-Defined Hardware-Assisted Verification to Enable AI Proliferation

Synopsys announced advancements across its industry-leading hardware-assisted verification (HAV) portfolio for customers to keep pace with continued, unprecedented demand for AI compute and related verification productivity to deliver multi-die and AI chips from the data center to the edge. Powered by the company's unique software-defined capabilities, Synopsys' HAV platforms set new performance, scalability, and flexibility benchmarks throughout the portfolio.

The company's software‑defined approach provides up to 2x higher performance on ZeBu Server 5 and up to 2x capacity scaling for modular HAV systems targeting AI‑era mega designs. Synopsys also launched the HAPS‑200 12 FPGA and ZeBu‑200 12 FPGA platforms for mainstream designs, offering EP‑Ready Hardware, 2x capacity, and continued leadership in software/hardware validation, power/performance analysis, and RTL verification. New, industry‑first test automation enables faster, earlier detection of cache‑coherency and subsystem‑level bugs. Synopsys is showcasing new HAV engines at Converge. Learn more here.

Launching Electronics Digital Twin Platform to Accelerate Physical AI System Development

Also, this week at Embedded World, Synopsys announced the Electronics Digital Twins (eDT) Platform. The eDT Platform enables an end‑to‑end digital twin foundation to help engineering teams connect silicon designs to software behavior and full‑system validation from the earliest stages of development. The eDT Platform brings together the company's product and market leadership supplying virtual SoC models and large‑scale system simulations, along with its extensive partner ecosystem, to simplify, accelerate, and scale the development of physical AI systems.

Initially focused on automotive use cases, the eDT Platform enables OEMs to achieve up to 90% of software validation prior to hardware availability by shifting software development and system integration "left," reducing vehicle development cost and time-to-market. Synopsys is demonstrating the new eDT Platform at Converge. Learn more here.

Follow Synopsys Converge 2026 News and Updates

Synopsys Converge is taking place March 11-12, 2026, at the Santa Clara Convention Center. Watch Sassine Ghazi's opening keynote and follow related news via the Synopsys Converge Newsroom, on LinkedIn, and on X.

About Synopsys

Synopsys, Inc. (Nasdaq: SNPS) is the leader in engineering solutions from silicon to systems, enabling customers to rapidly innovate AI-powered products. We deliver industry-leading silicon design, IP, simulation and analysis solutions, and design services. We partner closely with our customers across a wide range of industries to maximize their R&D capability and productivity, powering innovation today that ignites the ingenuity of tomorrow. Learn more at www.synopsys.com.

© 2026 Synopsys, Inc. All rights reserved. Synopsys, Ansys, the Synopsys and Ansys logos, and other Synopsys trademarks are available at https://www.synopsys.com/company/legal/trademarks-brands.html. Other company or product names may be trademarks of their respective owners.

Contacts

Media

Kelli Wheeler: kelliw@synopsys.com

Pete Smith: pete.smith@synopsys.com

corp-pr@synopsys.com

Investors

Tushar Jain

Synopsys-ir@synopsys.com

![]() View original content to download multimedia:https://www.prnewswire.com/news-releases/synopsys-outlines-vision-for-engineering-the-future-302711205.html

View original content to download multimedia:https://www.prnewswire.com/news-releases/synopsys-outlines-vision-for-engineering-the-future-302711205.html

SOURCE Synopsys, Inc.

New product capabilities deliver leading performance, capacity, and industry-first hardware-assisted test-automation capabilities to accelerate AI silicon innovation from data center to edge

Key Highlights

- Software-defined approach enables an up to 2x performance boost for ZeBu Server 5 and scales capacity up to 2x with modular HAV for AI-era mega designs

- New HAPS-200 12 FPGA and ZeBu-200 12 FPGA platforms for mainstream designs feature EP‑Ready Hardware that extends emulation and prototyping capacity by 2x and delivers leading performance for emulation and prototyping use cases

- New, industry-first hardware-assisted test automation capabilities enable faster, earlier detection of cache‑coherency and subsystem‑level bugs for maximum coverage

SUNNYVALE, Calif., March 11, 2026 /PRNewswire/ -- Synopsys, Inc. (Nasdaq: SNPS) today announced advancements across its leading hardware-assisted verification (HAV) portfolio, including new hardware platforms and capabilities to support the ever-expanding demand for AI chip verification from the data center to the edge. Synopsys HAV platforms, powered by the company's unique software-defined capabilities, set new performance, scalability, and use case benchmarks for verifying the world's most sophisticated multi-die and AI chips amidst compounding design complexity and time-to-market requirements.

AI chip verification complexity is escalating rapidly as large language models continue to double in size roughly every four months, and interface data rates advance at a 2x rate every three years. Simultaneously, edge AI architectures are driving aggressive throughput, latency, and power‑efficiency targets that further expand the design and validation workload. To keep pace, the industry requires HAV solutions to support broader application coverage and run quadrillions of verification cycles, enabling first‑time‑right silicon and a seamless ability to integrate heterogeneous AI systems.

"As AI-driven systems become more complex, verification must scale just as quickly. Hardware-assisted verification is no longer optional. It is critical to meeting aggressive time-to-market goals and ensuring silicon readiness," said Salil Raje, Senior Vice President and General Manager, Adaptive and Embedded Computing Group, AMD. "FPGA-based emulation and prototyping play a central role in that effort by accelerating system bring-up and enabling earlier software development. Our collaboration with Synopsys reflects that focus. Through joint optimization of Synopsys ZeBu with the AMD Vivado™ software stack, and by leveraging AMD EPYC™ processors for compute acceleration, we are reducing compile times and helping customers move to accurate system models faster."

"As AI becomes more pervasive across almost every industry and products are now workload-optimized and silicon-powered, building high confidence early that the workloads are running to spec on the silicon under development is critical," said Ravi Subramanian, Chief Product Management Officer at Synopsys. "Our software-defined, hardware-assisted verification solutions deliver continuous innovation. They are a powerful force multiplier to scale verification productivity and meet the growing demand for pre-silicon development across industries."

The latest advancements across Synopsys' software-defined hardware-assisted verification portfolio, include:

Breakthrough performance and capacity for the AI era: The latest software-defined updates and modular HAV are available across the ZeBu and HAPS platforms. Of note, with these updates, the industry's highest capacity-scalable emulation platform, ZeBu Server 5, supports complex designs to meet the demands of mega designs supporting data center AI training and inference, GPU, custom accelerators, and networking IPU/DPU workloads. Modular HAV for HAPS enables the largest prototypes for software development, with further improvements for compute, storage, and bring-up capabilities.

New HAPS and ZeBu platforms: The new HAPS-200 12 FPGA and ZeBu-200 12 FPGA systems address the complexity and high-performance requirements for data center-sub-system, mobile, client, server, consumer, and edge AI applications. They deliver 2x higher capacity compared to previous 6 FPGA platforms utilizing the flagship AMD Versal™ Premium VP1902 adaptive SoCs, offering EP-Ready Hardware-enabled configurability between prototyping and emulation. Synopsys also introduces the new HAPS-200 1 FPGA platform as a desktop system ideal for IP verification and software bring-up using Synopsys Interface Prototyping Kits.

"As NVIDIA's AI platforms have become software‑defined to meet rising performance and scalability demands, verification must evolve in the same way," said Narendra Konda, Vice President, Hardware Engineering at NVIDIA. "Synopsys' software‑defined hardware‑assisted verification and the new HAPS‑200 12 FPGA systems are accelerating our system‑level verification and validation, helping us deliver complex AI platforms on aggressive schedules. And, Synopsys modular hardware-assisted verification enables deeper collaboration across our ecosystem."

Software-defined HAV capabilities extend system lifetime value: Continuous software improvements deliver compounding performance gains, increased debug productivity, as well as additional use case capabilities for both new and installed systems. The Synopsys HAV portfolio supports new, industry-first Hardware-Assisted Test Solutions, test automation capabilities that allow teams to stress corner cases for processor, memory, and I/O subsystems as well as full-system coherency validation and observe system behavior under realistic workloads in emulation long before silicon is ready. For mixed-signal and system-level designs, Real-Number Models (RNM) emulation enables fast, scalable abstraction of analog behavior within digital-centric verification flows for faster software bring-up. For safety-critical and high-reliability designs, new fault emulation capabilities enable scalable fault injection and analysis across RTL simulation, emulation, and prototyping.

"Verifying hardware for our highly anticipated rack-scale AMD Helios solution – marked by massive AI scale, complex subsystems, and robust software stacks – demands scalable and versatile verification platforms," said Alex Starr, Corporate Fellow, AMD. "The Synopsys software-defined, HAV capabilities with EP-Ready Hardware are critical to how we perform CPU, GPU, and AI subsystems verification as well as full-system validation. Teams can also cover an expanded number of use cases in the pre-silicon phase, encompassing analog, digital, and software design verification using Real-Number Models (RNM) in emulation. As well, the flexibility to reconfigure and reuse hardware across projects and move seamlessly between emulation and prototyping as AI designs grow in both physical size and software stack volume are essential to delivering the high-performance, interoperable AI infrastructure at scale needed to meet the world's growing AI demands."

Availability & Additional Resources

Software-defined enhancements are being rolled out continuously across the HAV portfolio, with the new capabilities available to users today. The new EP‑Ready HAPS-200 12 FPGA and ZeBu-200 12 FPGA platforms are available today and in Q3 2026, respectively. HAPS-200 1 FPGA platform is available today.

- Product Page: Synopsys HAV Solutions Family

- Blog: Introducing Software-Defined Hardware-Assisted Verification: A New Benchmark for AI-Era Chip Design

- Video: Software-Defined Hardware-Assisted Verification for the AI Era

Follow Synopsys Converge 2026 News and Updates

Synopsys Converge is taking place March 11-12, 2026, at the Santa Clara Convention Center. Follow news and updates as well as keynote details and replays via the Synopsys Converge Newsroom, on LinkedIn, and on X.

About Synopsys

Synopsys, Inc. (Nasdaq: SNPS) is the leader in engineering solutions from silicon to systems, enabling customers to rapidly innovate AI-powered products. We deliver industry-leading silicon design, IP, simulation and analysis solutions, and design services. We partner closely with our customers across a wide range of industries to maximize their R&D capability and productivity, powering innovation today that ignites the ingenuity of tomorrow. Learn more at www.synopsys.com.

© 2026 Synopsys, Inc. All rights reserved. Synopsys, Ansys, the Synopsys and Ansys logos, and other Synopsys trademarks are available at https://www.synopsys.com/company/legal/trademarks-brands.html. AMD EPYC, Versal, Vivado and combinations thereof are trademarks of Advanced Micro Devices, Inc. Other company or product names may be trademarks of their respective owners.

Contacts

Media

Kelli Wheeler: kelliw@synopsys.com

Pete Smith: pete.smith@synopsys.com

corp-pr@synopsys.com

![]() View original content to download multimedia:https://www.prnewswire.com/news-releases/synopsys-introduces-software-defined-hardware-assisted-verification-to-enable-ai-proliferation-302711214.html

View original content to download multimedia:https://www.prnewswire.com/news-releases/synopsys-introduces-software-defined-hardware-assisted-verification-to-enable-ai-proliferation-302711214.html

SOURCE Synopsys, Inc.